高速PCB铺铜到底怎么铺

在日常PCB设计中,我们经常会看到整版大面积铺铜,看起来既专业又美观,好像已经成了“默认操作”。但你真的了解这样做的后果吗?尤其是在电源类板子和高速信号板中,铺铜可不是越多越好,处理不好反而会影响电气性能甚至埋下安全隐患!

今天我们就来详细聊聊——

不同类型PCB该怎么铺铜?

铺铜距离对阻抗的影响有多大?

如何正确设置铜皮间距?

电源类PCB:铺铜≠屏蔽,反而可能是“雷区”!

电源板电流大、电压高,我们在设计时经常需要预留爬电间距,尤其是高压与低压之间更要严格区分。此时如果大面积铺铜,很多时候会变成碎铜,这些碎铜不但起不到屏蔽作用,反而可能成为干扰源。

建议:

电源类PCB铺铜要慎重,不要盲目整版铺铜,优先考虑安全间距与EMC设计。

高速PCB:铜皮与阻抗线的“微妙关系”

高速信号讲究阻抗控制,如果你随意把铜皮铺得太近,就可能大幅改变线的阻抗,从而导致信号反射、失真、EMI等问题。

实验验证:

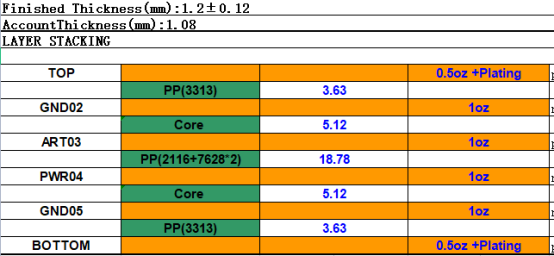

我们使用以下叠层结构进行仿真分析:

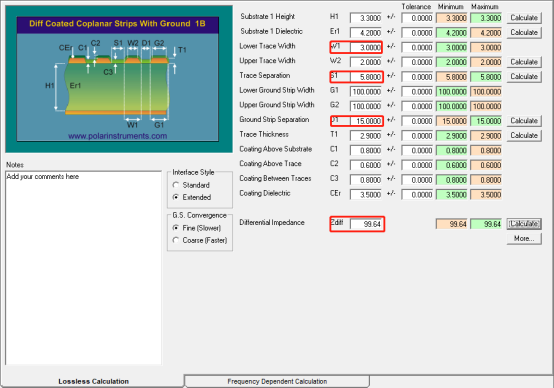

图1:叠层结构 我们计算了表层与内层100Ω差分线的线宽和线距:

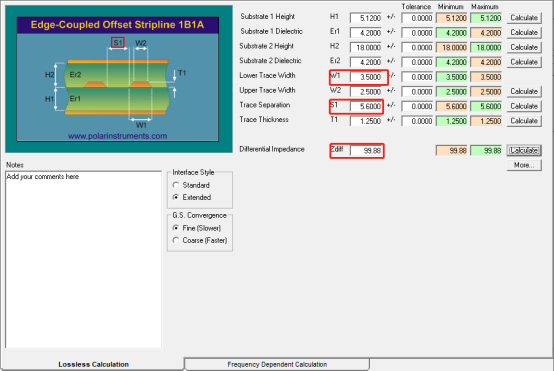

图2:表层计算结果

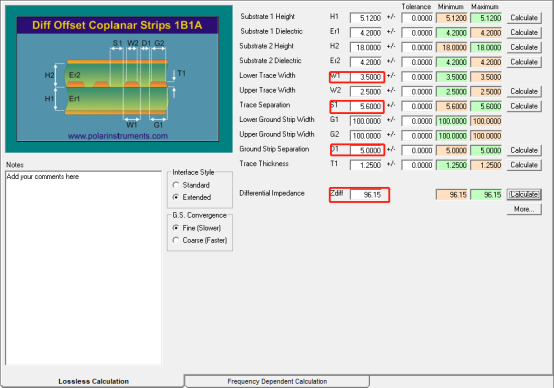

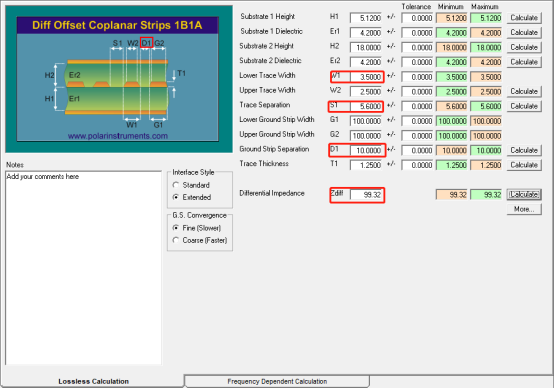

图3:内层计算结果

表层差分线宽/距为 3mil/5.8mil,内层为 3.5mil/5.6mil。

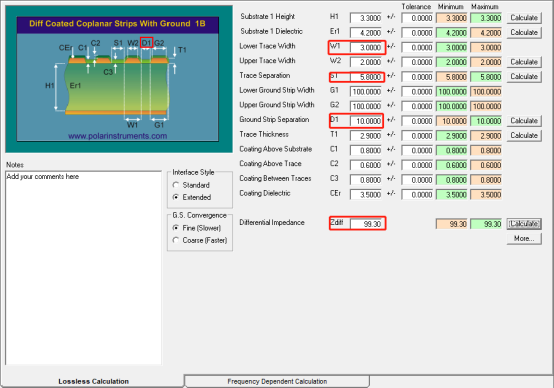

然后我们模拟在差分线两侧铺上铜皮的情况,铜皮距离为5mil,看看对阻抗的影响:

图4、图5:铜皮距离5mil下的阻抗变化 结果: 不论外层还是内层,差分阻抗都下降了约 3Ω!

间距设置多少才合适?我们继续测试!

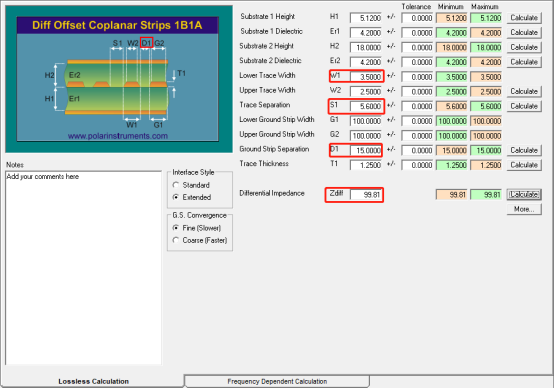

进一步仿真铜皮离差分线 10mil和15mil 时的影响:

图6 ~ 图9:间距变化下的仿真对比

结论非常直观:

距离10mil时,仍有约0.5Ω的下降

距离15mil时,阻抗变化可忽略不计!

实战建议总结:

铜皮与阻抗线的间距至少15mil以上

1、空间允许时建议设置为20mil更保险

2、避免整版铺铜,可使用网格或小块铺铜方式补强

3、关注DRC规则设置,提前预警铜皮距离

写在最后

别再把铺铜当“装修工程”了!真正专业的高速PCB设计,关键在于每一个细节处理。你可能看不到它,但信号完整性、EMC表现却会如实反映每一次轻率铺铜的代价。

本文凡亿教育原创文章,转载请注明来源!

域财网

域财网